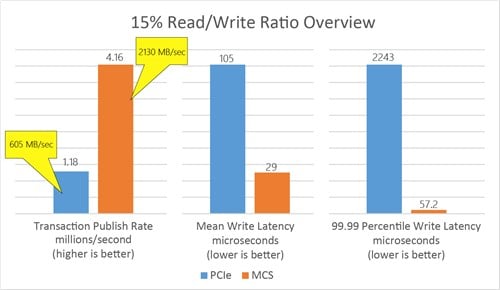

Today, 60East is announcing the results of our evaluation of Memory Channel Storage™ (MCS™) architecture from Diablo Technologies, Incorporated at the Flash Memory Summit. In our labs, MCS demonstrated very low latency with a consistent latency profile and high throughput, as shown in the chart below and described in more detail in our new information sheet.

MCS uses NAND Flash memory to provide storage directly in the CPU memory subsystem – effectively replacing DIMMs containing RAM with persistent storage. At 60East, we’re both hardware enthusiasts and performance engineers. As enthusiasts, we loved the idea. As performance engineers, we know that great ideas are only valuable when they deliver measurable benefits in real workloads. We wanted to know more about the MCS architecture, to evaluate it, and to see how the technology would work for customers. Getting our hands on the hardware was the first step to understanding it and squeezing every bit of performance out of it.

60East invited Diablo into our performance lab to test MCS, using the AMPS I/O engine to push the limits of the system in the same ways that our customers do. First, 60East and Diablo set up a test evaluating full speed writing of 512 byte messages (batched in 64KB chunks), using MCS in the same way transactional messaging does. Then, we ran tests evaluating mixes of reads and writes, to look at performance in a workload that mixes bookmark replays (simultaneous sequential reads from elsewhere on the device) in with transactional messaging. Read/write mixes are difficult workloads for most storage systems, and can dramatically change latency and throughput compared to write-only mixes.

In both tests, we were blown away by the overall performance and consistently low latency of MCS under these workloads. The chart says it all: at a mix that includes a realistic amount of reads, MCS consistently wrote more data at a fraction of the latency of the PCIe solution.

We’re thrilled to announce these results, and we’re looking forward to seeing systems using MCS going into production. As always, we’re learning more about MCS and about how the AMPS engine performs with MCS, and we are looking at ways to get the best performance out of the hardware.

Diablo is demonstrating our results at the Flash Memory Summit this week with Jeffrey M. Birnbaum, 60East’s co-Founder and CEO. Demonstration systems are located in the Smart Storage Systems exhibit, booth 202. Diablo will also be at VMWorld in San Francisco August 25-29.